Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

The equations and analysis of mos transistor characteristics using a simple analytic model. It also covers the design of a cmos inverter and the calculation of noise margins.

Typology: Exercises

1 / 35

This page cannot be seen from the preview

Don't miss anything!

In this booklet, we shall use simple analytical models for MOS transistors. We use a sign convention according to which, voltage and current symbols associated with the pMOS transistor (such as VT p) have positive values. Then, the n channel formulae can be used for both transistors and we shall assign signs to quantities explicitly.

Drain Current (mA)

Drain Voltage (V)

Vg = 3.

Figure 1.1: MOS characteristics according to the simple analytic model

The model we use is described by the following equations: for Vgs ≤ VT, Ids = 0 (1.1)

for Vgs > VT and Vds ≤ Vgs − VT,

Ids = K

[ (Vgs − VT )Vds −

V (^) ds^2

] (1.2)

and for Vgs > VT and Vds > Vgs − VT,

Ids = K

(Vgs − VT )^2 2

The saturation region equation is somewhat oversimplified because it assumes that the current is independent of Vds. In reality, the current has a weak dependence on Vds in this region.

In order to model the saturation region more accurately, we adopt an “Early Voltage” like formalism.

Figure 1.2: MOS characteristics with non zero conductance in saturation

It is assumed that the current increases linearly in the saturation region. All linear

Characteristics of a MOS transistor using this model are shown in fig.1.2. While accurate modeling of the output conductance is essential for linear design, the simpler model assuming constant Id in saturation is often adequate for preliminary digital design. In any case, final designs will have to be validated with detailed simulations. In this booklet, we shall use the simple model for MOS devices to keep the algebra simple.

Static logic circuits are those which can hold their output logic levels for indefinite periods as long as the inputs are unchanged. Circuits which depend on charge storage on capacitors are called dynamic circuits and will be discussed in a later chapter.

The most common design style in modern VLSI design is the Static CMOS logic style. In this, each logic stage contains pull up and pull down networks which are controlled by input signals. The pull up network contains p channel transistors, whereas the pull down network is made of n channel transistors. The networks are so designed that the pull up and pull down networks are never ‘on’ simultaneously. This ensures that there is no static power consumption.

The simplest of such logic structures is the CMOS inverter. In fact, for any CMOS logic design, the CMOS inverter is the basic gate which is first analyzed and designed in detail. Thumb rules are then used to convert this design to other more complex logic. The basic CMOS inverter is shown in fig. 2.1. We shall develop the characteristics of CMOS logic through the inverter structure, and later discuss ways of converting this basic structure more complex logic gates.

The range of input voltages can be divided into several regions.

These equations are valid only when the pMOS is in its linear regime. This requires that Vdp ≡ Vdd − Vo ≤ Vdd − Vi − VT p

Therefore, we must choose the negative sign. Thus

Vdd − Vo = (Vdd − Vi − VT p) −

√ Vdd − Vi − VT p)^2 − β(Vi − VT n)^2 (2.5)

Therefore,

Vo = Vi + VT p +

√ (Vdd − Vi − VT p)^2 − β(Vi − VT n)^2 (2.6)

Since Vo must be ≥ Vi + VT p, the limit of applicability of the above result is given by (Vdd − Vi − VT p)^2 = β(Vi − VT n)^2

That is, the solution for Vo is valid for

Vi ≤

Vdd +

βVT n − VT p 1 +

β

In the case where we size the n and p channel transistors such that

Kn = Kp; so β = 1

we have

Vo = (Vi + VT p) +

√ (Vdd − VT n − VT p)(Vdd − 2 Vi + VT n − VT p) (2.8)

with

Vi ≤

Vdd + VT n − VT p 2

nMOS saturated, pMOS saturated

At the limit of applicability of eq. 2.7, when the input voltage is exactly at

Vi =

Vdd +

βVT n − VT p 1 +

β

both transistors are saturated. Since the currents of both transistors are indepen- dent of their drain voltages in this condition, we do not get a unique solution for Vo by equating drain currents. The currents will be equal for all values of Vo in the range Vi − VT n ≤ Vo ≤ Vi + VT p

Thus the transfer curve of an inverter shows a drop of VT n+ VT p at a voltage near Vdd/2. This is actually an artifact of the simple transistor model chosen for this

0.

3.

2.

2.

1.

1.

0.

V

V

oH

oL 0.0 0.5 1.0 1.5 2.0 2.5 3. ViL ViH Input Voltage

Output Voltage

VTn +V Tp

Figure 2.2: Transfer Curve of a CMOS inverter

analysis, which assumes perfect saturation of drain current. In a real case, the drain current does depend on the drain voltage (albeit weakly) in the saturation region. If the model incorporates an Early Voltage like effect, the drop near the middle of the characteristic is more gradual.

nMOS linear, pMOS saturated

At the gate voltage given by eq. 2.9, both transistors are saturated. As we increase Vi beyond this value, such that

Vdd +

βVT n − VT p 1 +

β

< Vi < Vdd − VT p

both transistors are still ‘on’, but nMOS enters the linear regime while pMOS gets saturated. Equating currents in this condition,

Id =

Kp 2

(Vdd − Vi − VT p)^2 = Kn

[ (Vi − VT n)Vo −

V (^) o^2

] (2.10)

From this, we get the quadratic equation

1 2

V (^) o^2 − (Vi − VT n)Vo +

(Vdd − Vi − VT p)^2 2 β

the flat portions of the transfer curve (where ∂V ∂Voi is small) are suitable for digital

logic. We select two points on the transfer curve where the slope (∂V ∂Voi ) is -1.0. The coordinates of these two points define the values of (ViL,VoH ) and (ViH ,VoL). Robust digital design requires that the output high level be higher than what is acceptable as a high level at the input (VoH > ViH ). The difference between these two levels is the ‘high’ noise margin. This is the amount of noise that can ride on the worst case ‘high’ output and still be accepted as a ‘high’ at the input of the next gate. Similarly, we require VoL < ViL. The difference, ViL − VoL is the ‘low’ noise margin. Obviously, it is of interest to evaluate the values of these noise margins. For the discussion which follows, we shall use the expressions derived earlier for β = 1 to keep the algebra simple.

Calculation of ViL and VoH

from eq. (2.8)

Vo = (Vi + VT p) +

√ (Vdd − VT n − VT p)(Vdd + VT n − VT p − 2 Vi)

From this, we can evaluate ∂V ∂Voi and set it = -1.

∂Vo ∂Vi

√ Vdd − VT n − VT p Vdd + VT n − VT p − 2 Vi

This gives

ViL =

3 Vdd + 5VT n − 3 VT p 8

Substituting this in eq.(2.8), we get

VoH =

7 Vdd + VT n + VT p 8

= Vdd −

Vdd − VT n − VT p 8

Calculation of ViH and VoL

When the input is ‘high’, we should use eq.(2.14).

Vo = (Vi − VT n) −

√ (Vdd − VT n − VT p)(2Vi − Vdd − VT n + VT p)

Differentiating with respect to Vi gives

∂Vo ∂Vi

√ Vdd − VT n − VT p 2 Vi − Vdd − VT n + VT p

From where, we get

ViH =

5 Vdd + 3VT n − 5 VT p 8

and

VoL =

Vdd − VT n − VT p 8

Calculation of Noise Margins

The high noise margin is given by

VoH − ViH =

Vdd − VT n + 3VT p 4

Similarly, the Low noise margin is

ViL − VoL =

Vdd + 3VT n − VT p 4

The two noise margins can be made equal by choosing equal values for VT n and VT p.

In this section, we analyze the dynamic behaviour of the inverter. For the calcu- lation of rise and fall times, we shall assume that only one of the two transistors in the inverter is ‘on’. (Notice that this is more conservative than the input high and low conditions determined by slope considerations in eq.2.19 and 2.16). We shall continue to use the simple model described at the beginning of this booklet.

Rise time

When the input is low, the n channel transistor is ‘off’, while the p channel tran- sistor is ‘on’. The equivalent circuit in this condition is shown in fig. 2.3. From

ViL

Vo

Vdd

Figure 2.3: CMOS inverter with the nMOS ‘off’

or

Kpτrise 2 C

ViL + VT p (Vdd − ViL − VT p)^2

2(Vdd − ViL − VT p)

ln

2 V 2 − Vdd + VoH Vdd − VoH

Thus,

τrise =

C(ViL + VT p) Kp 2 (Vdd^ −^ ViL^ −^ VT p)

2

Kp(Vdd − ViL − VT p)

ln

Vdd + VoH − 2 ViL − 2 VT p Vdd − VoH

The first term is just the constant current charging of the load capacitor. The second term represents the charging by the pMOS in its linear range. This can be compared with resistive charging, which would have taken a charge time of

τ = RC ln

Vdd − ViL − VT p Vdd − VoH

to charge from ViL+ VT p to VoH.

Fall time

When the input is high, the n channel transistor is ‘on’ and the p channel transistor is ‘off’. If the output was initially ‘high’, it will be discharged to ground through

Vo Vi H

Figure 2.4: CMOS inverter with the pMOS ‘off’

the nMOS. To analysis the fall time, we apply Kirchoff’s current law to the output node. This gives

Idn = −C

dVo dt

Again, separating variables and integrating from the initial voltage (= Vdd) to some terminal voltage VoL gives τf all C

∫ (^) voL

Vdd

dVo Idn

The n channel transistor will be in saturation till the output voltage falls to Vi- VT n. Below this voltage, the transistor will be in its linear regime. Thus, we can divide the integration range in two parts.

τf all C

∫ (^) Vi−VT n

Vdd

dVo Idn

∫ (^) VoL

Vi−VT n

dVo Idn

=

∫ (^) Vdd

Vi−VT n

dVo Kn 2 (Vi^ −^ VT n)

2

∫ (^) Vi−VT n

VoL

dVo Kn[(Vi − VT n)Vo − 12 V (^) o^2

Therefore

Knτf all 2 C

Vdd − Vi + VT n (Vi − VT n)^2

∫ (^) Vi−VT n

VoL

dVo 2 Vo(Vi − VT n) − V (^) o^2

=

Vdd − Vi + VT n (Vi − VT n)^2

2(Vi − VT n)

∫ (^) Vi−VT n

VoL

dVo

( 1 Vo

2(Vi − VT n) − Vo

)

Which gives

Knτf all 2 C

Vdd − Vi + VT n (Vi − VT n)^2

2(Vi − VT n)

[ ln

Vo 2(Vi − VT n) − Vo

]Vi−VT n

VoL

=

Vdd − Vi + VT n (Vi − VT n)^2

2(Vi − VT n)

ln

2(Vi − VT n) − VoL VoL

and therefore

τf all =

C(Vdd − Vi + VT n) Kn 2 (Vi^ −^ VT n)

Kn(Vi − VT n)

ln

2(Vi − VT n) − VoL VoL

Again, the first term represents the time taken to discharge at constant current in the saturation regime, whereas the second term is the quasi-resistive discharge in the linear regime.

As we scale technologies, we improve speed and power consumption. However, as we can see from the expression for noise margins, (eq 2.21 and eq 2.22) the noise margin becomes worse. We can improve noise margins by choosing relatively higher threshold voltages. However, this will reduce speeds. We could also increase Vdd- but that would increase power dissipation. Thus we have a trade off between power, speed and noise margins. This choice is made much more complicated by process variations, because we have to design for the worst case.

A

C

B

D E Out A

B

C

D (^) E

Vdd

Figure 2.5: CMOS implementation of A.B + C.(D + E)

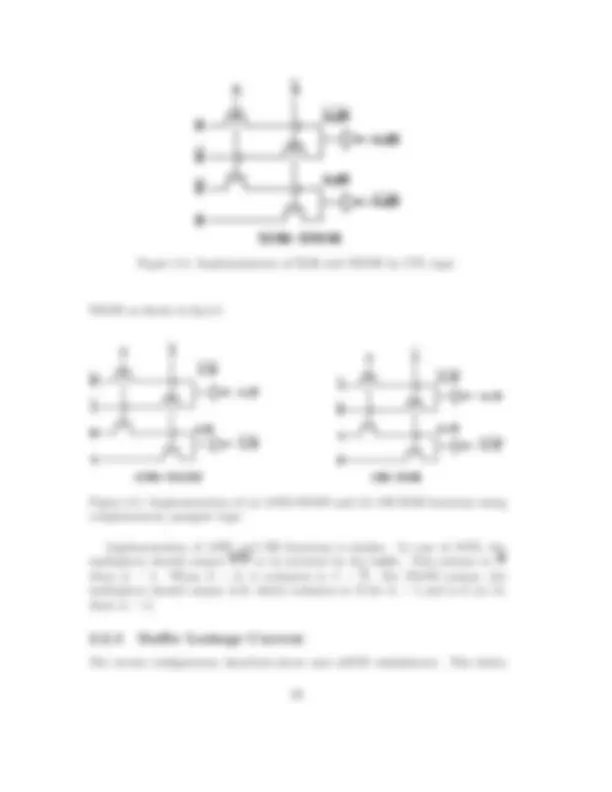

CMOS design style ensures that the logic consumes no static power. This is be- cause the pull down and pull up networks are never ‘on’ simultaneously. However, this requires that signals have to be routed to the n pull down network as well as to the p pull up network. This means that the load presented to every driver is high. This fact is exacerbated by the fact that n and p channel transistors cannot be placed close together as these are in different wells which have to be kept well separated in order to avoid latchup.

Pseudo nMOS design style reduces dynamic power (by reducing capacitive loading) at the cost of having non-zero static power by replacing the pull up network by a single pMOS transistor with its gate terminal grounded. The pseudo nMOS inverter is shown below.

Vdd

Gnd

Out

in

Notice that since the pMOS is not driven by signals, it is always ‘on’. The effective gate voltage seen by the pMOS transistor is Vdd. Thus the overvoltage on the p channel gate is always Vdd- VT p. When the nMOS is turned ‘on’, a direct path between supply and ground exists and static power will be drawn.